#### INCREASING SELF-TIMED CIRCUIT SOFT ERROR TOLERANCE

#### Igor Sokolov, Yury Stepchenkov, Yury Diachenko, Yury Rogdestvenski, and Denis Diachenko

Federal Research Center "Computer Science and Control" of the Russian Academy of Sciences, FRC CSC RAS, Moscow, Russian Federation

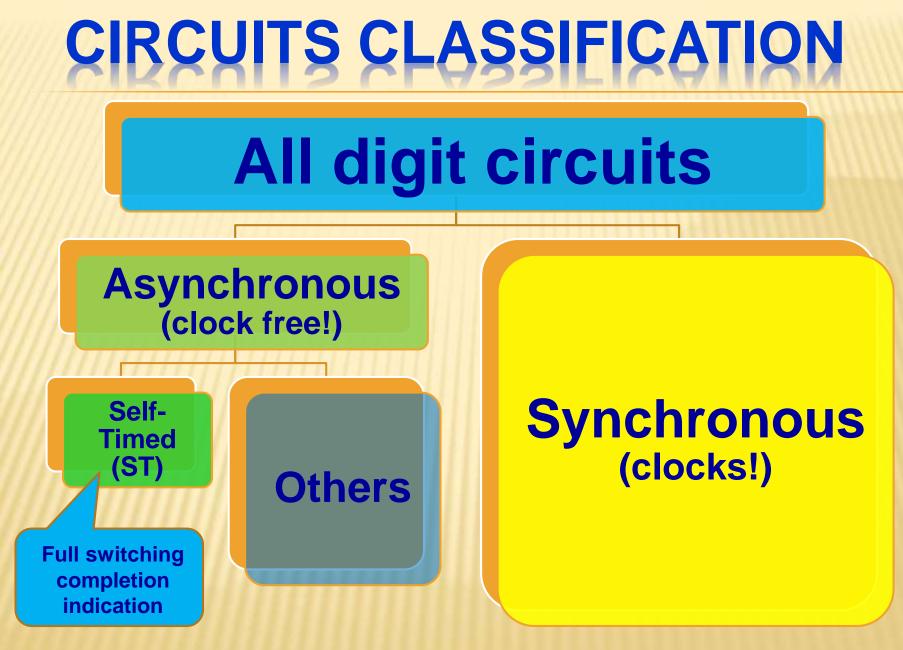

### OUTLINE

- Synchronous and Self-Timed circuits

- Self-Timed circuit's soft-error tolerance

- Indication subcircuit implementation

- How to increase indication subcircuit immunity to soft-errors?

- Conclusions

FRC CSC RAS

**EWDTS-2020**

FRC CSC RAS

**EWDTS-2020**

#### **SELF-TIMER PRINCIPLES**

- Two operation phase:

- \* work phase (data processing)

- \* spacer (pause)

- Dual-rail information signal coding in combinational circuits

- Full indication of all circuit's cells in each operation phase

FRC CSC RAS EWDTS-2020

# ST CIRCUIT'S FEATURES

#### **Advantages:**

- Their workability does not depend on delay of their cells and wires

- Extremely wide workability range on supply voltage and ambient temperature,

- Constant failure detection and localization

- High soft error immunity Draw-backs:

- Increased hardware complexity

- Lower performance in multi-bit data processing

FRC CSC RAS EWDTS-2020

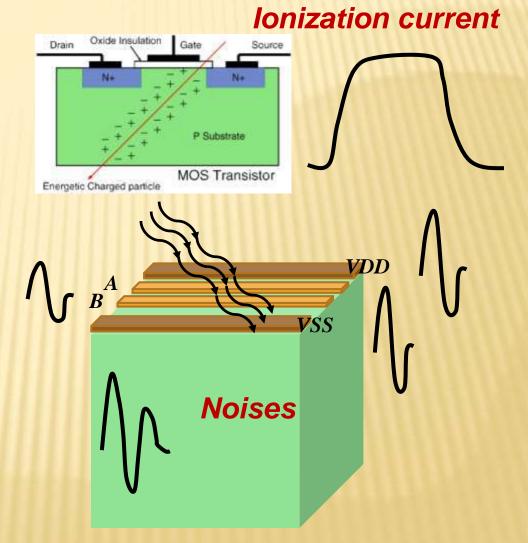

### SOFT ERROR SOURCES

- Nuclear particles and cosmic rays

- External electromagnetic pulse

- Cross-talks on signal wires

- Noise on power stripes

- Substrate noises

FRC CSC RAS

**EWDTS-2020**

### **DUAL-RAIL CODING**

#### Two work states and one spacer

| Dual-rail<br>value                                                 | Spacer type |             |

|--------------------------------------------------------------------|-------------|-------------|

|                                                                    | Null        | Unit        |

| 01                                                                 | Work state  | Work state  |

| 10                                                                 | Work state  | Work state  |

| 00                                                                 | Spacer      | Anti-spacer |

| 11                                                                 | Anti-spacer | Spacer      |

| Anti-spacer is a state inverse to spacer. It is usually prohibited |             |             |

FRC CSC RAS

**EWDTS-2020**

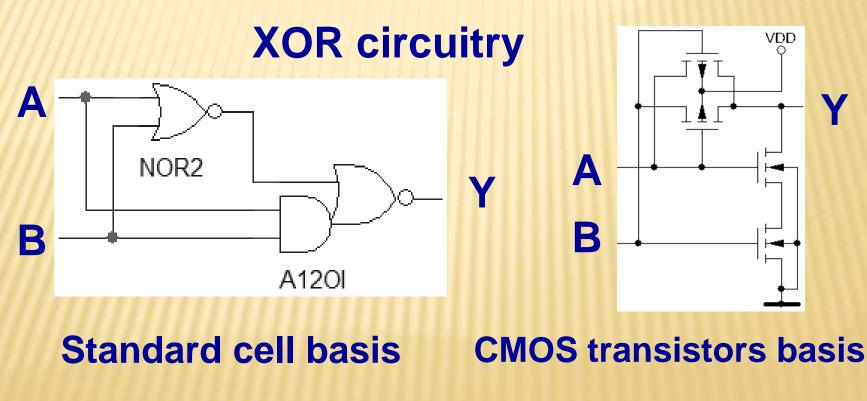

#### INDICATION SUBCIRCUIT BASIS

# Solution: Let's indicate anti-spacer as the second spacer by XOR / XNOR cell

FRC CSC RAS

**EWDTS-2020**

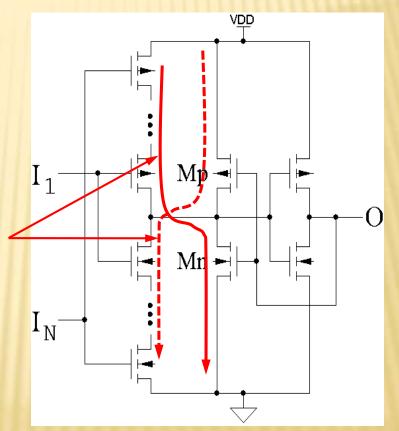

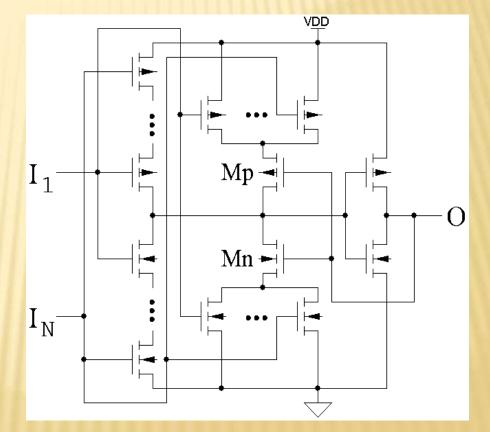

#### INDICATION CIRCUITRY

$$O^{+} = I_{1} \cdot I_{2} \cdot \ldots \cdot I_{N} + O \cdot (I_{1} + I_{2} + \ldots + I_{N})$$

Semi-static Muller's C-element:

+ Short-circuit current when switching

-Minimal complexity

FRC CSC RAS

**EWDTS-2020**

#### INDICATION CIRCUITRY

$$O^{+} = I_{1} \cdot I_{2} \cdot \ldots \cdot I_{N} + O \cdot (I_{1} + I_{2} + \ldots + I_{N})$$

Static Muller's C-element or Hysteretic trigger:

+ Short-circuit current is absent

Increased complexity

FRC CSC RAS

**EWDTS-2020**

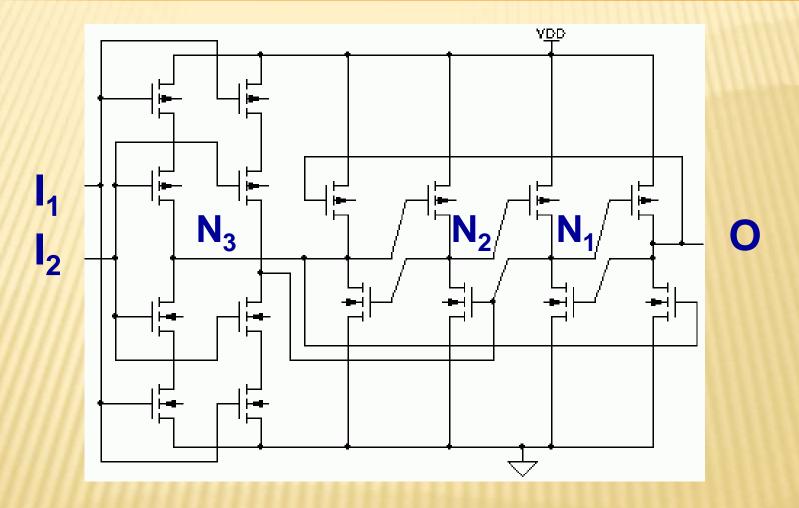

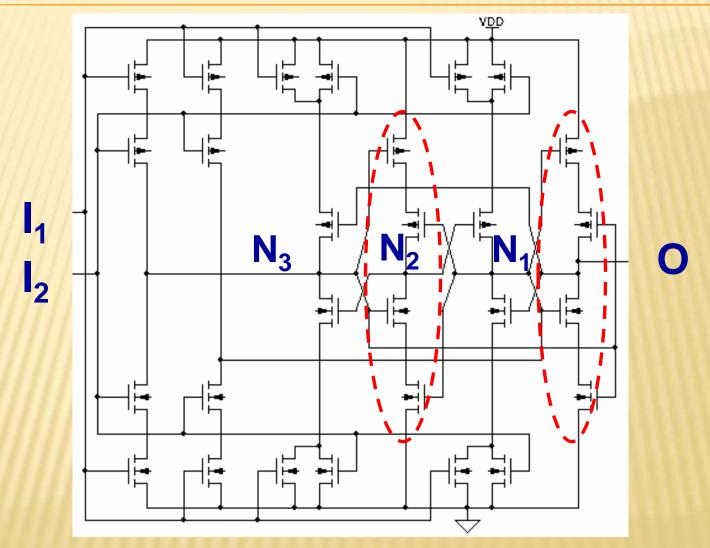

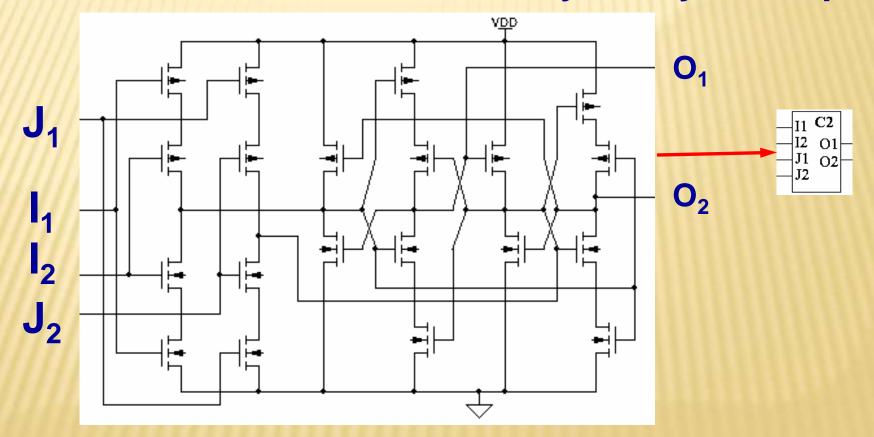

#### **PICE-LIKE SEMI-STATIC C-ELEMENT**

FRC CSC RAS

**EWDTS-2020**

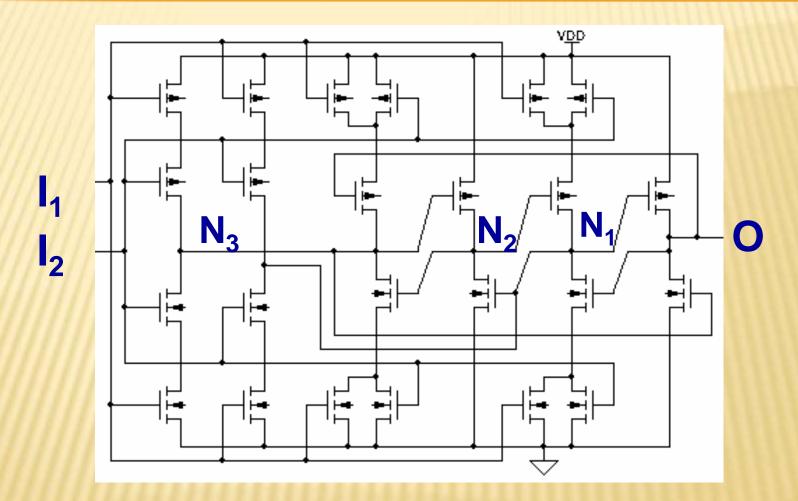

#### **DICE-LIKE STATIC C-ELEMENT**

FRC CSC RAS

**EWDTS-2020**

### **PICE-LIKE SEMI-STATIC C-ELEMENT**

FRC CSC RAS

**EWDTS-2020**

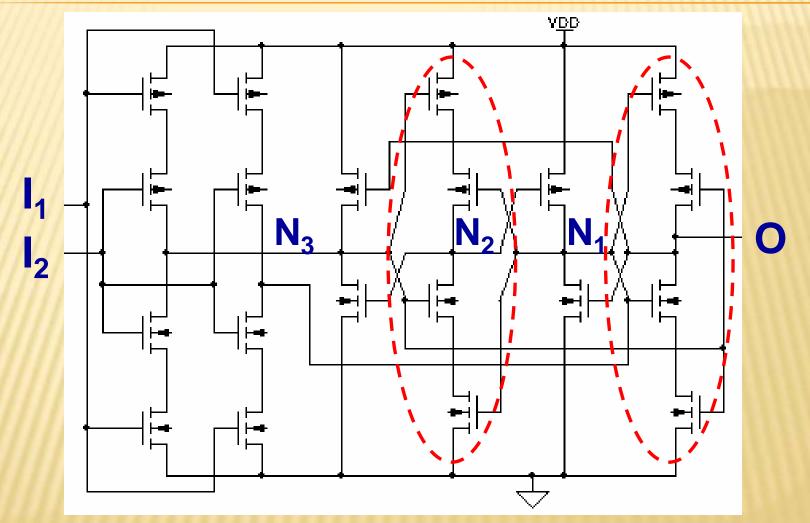

#### **DICE-LIKE STATIC C-ELEMENT**

FRC CSC RAS

**EWDTS-2020**

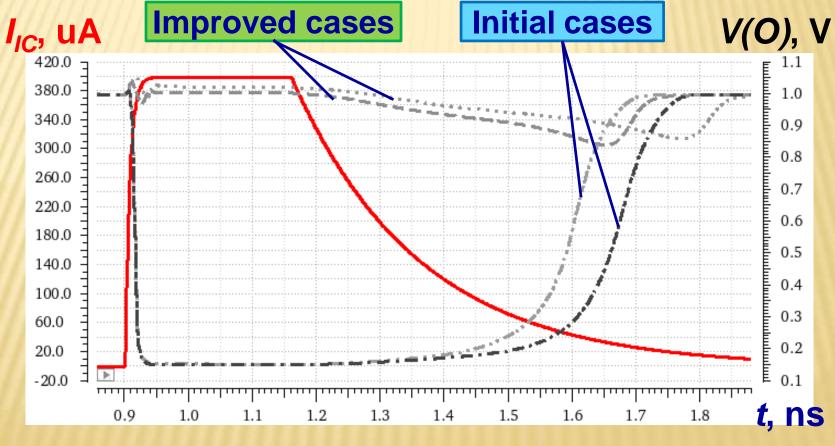

#### **C-ELEMENTS COMPARISON (1)**

The influence of ionization current pulse (A = 400 uA,  $t_R = 7$  ps,  $t_F = 200$  ps, "plateau" = 200 ps) at node N<sub>1</sub>

FRC CSC RAS

**EWDTS-2020**

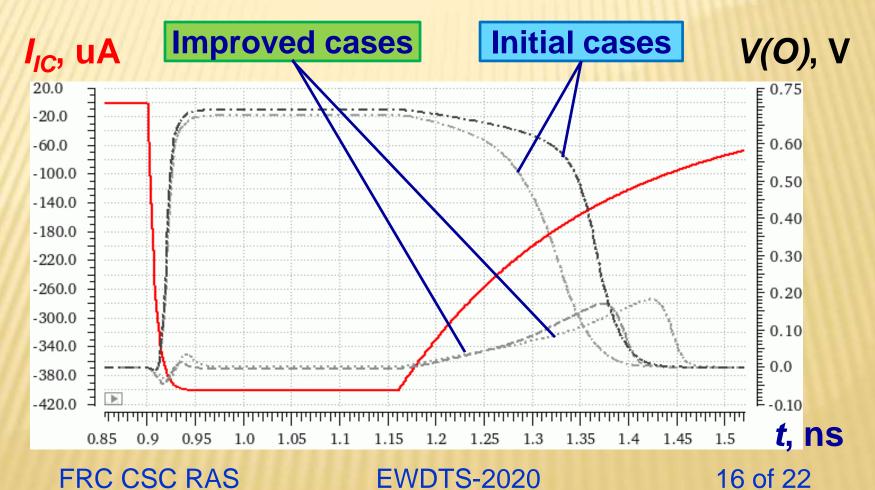

#### **C-ELEMENTS COMPARISON (2)**

The influence of ionization current pulse (A = -400 uA, t<sub>F</sub> = 7 ps, t<sub>R</sub> = 200 ps, "plateau" = 200 ps) at node N<sub>3</sub>

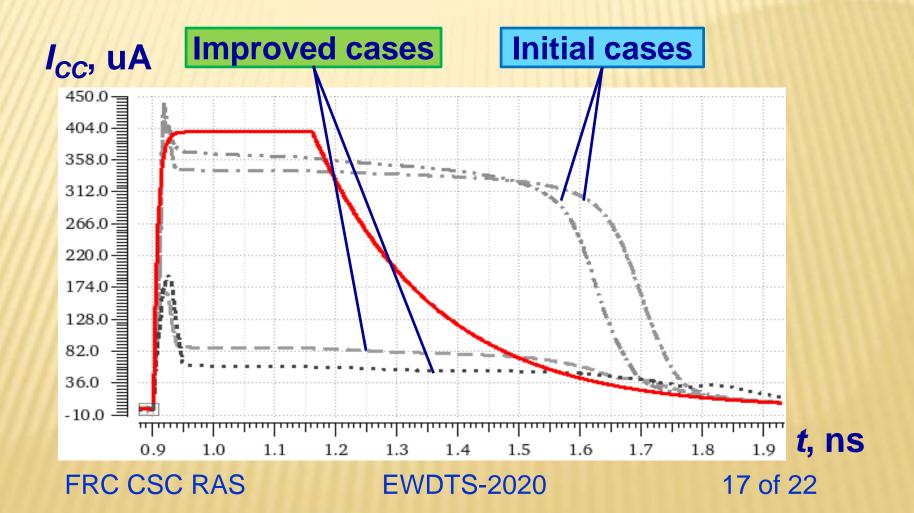

#### **C-ELEMENTS COMPARISON (3)**

#### **Consumption current during soft error**

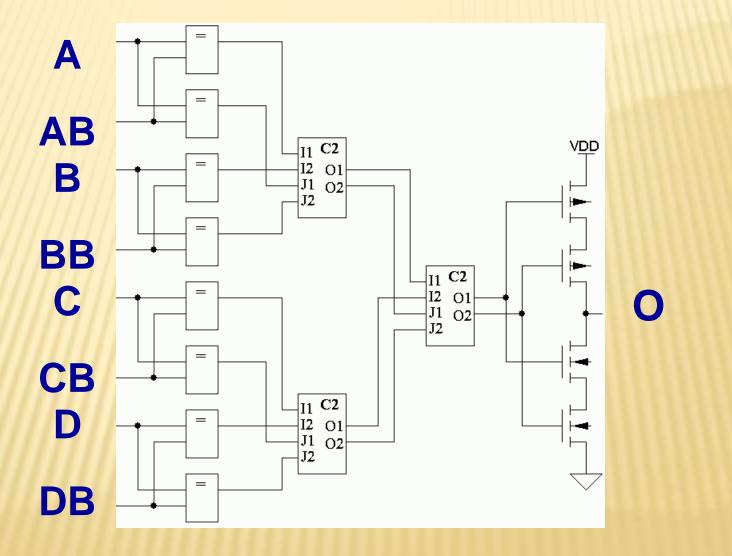

#### **IN-PHASE C-ELEMENTS**

C-element with in-phase input and output pairs masks soft error induced directly at any its output

FRC CSC RAS

**EWDTS-2020**

#### INDICATION SUBCIRCUIT STRUCTURE

FRC CSC RAS

**EWDTS-2020**

#### SUMMARY

- Soft error tolerance of the indication subcircuit largetly determines entire self-timed circuit's tolerance

- XOR or XNOR cells at the first stage of the indication subcircuit prevent the errors caused by anti-spacer state

- Four-transistor output cascade makes the DICE-like Celement entirely immune to single soft errors at its internal and input nodes

- The proposed indication subcircuit building technique doubles its hardware complexity but ensures its absolute immunity to the short-term soft errors

FRC CSC RAS

**EWDTS-2020**

# **Thank You!**

FRC CSC RAS

**EWDTS-2020**

## CONTACTS

- Director: academician Sokolov I.A.

- Address: Institute of Informatics Problems of the Federal Research Center "Computer Science and Control" of the Russian Academy of Sciences (IPI RAS), Moscow, Russian Federation, 119333, Vavilova str., 44, b.2

- Tel: +7 (495) 137 34 94

- Fax: +7 (495) 930 45 05

- E-mail: <u>ISokolov@ipiran.ru</u>

- Stepchenkov Y.A., tel. +7 (495) 671 15 20, Ystepchenkov@ipiran.ru

FRC CSC RAS

**EWDTS-2020**