# SELF-TIMED STORAGE REGISTER SOFT ERROR TOLERANCE IMPROVEMENT

### Yuri Stepchenkov, Yuri Diachenko, Yuri Rogdestvenski, Yuri Shikunov, and Denis Diachenko

Federal Research Center "Computer Science and Control" of the Russian Academy of Sciences, FRC CSC RAS, Moscow, Russian Federation

# OUTLINE

- What is a soft error?

- Self-timed circuits

- Soft error types

- Masking soft error in combinational part and register

- Summary

FRC CSC RAS

**EWDTS-2021**

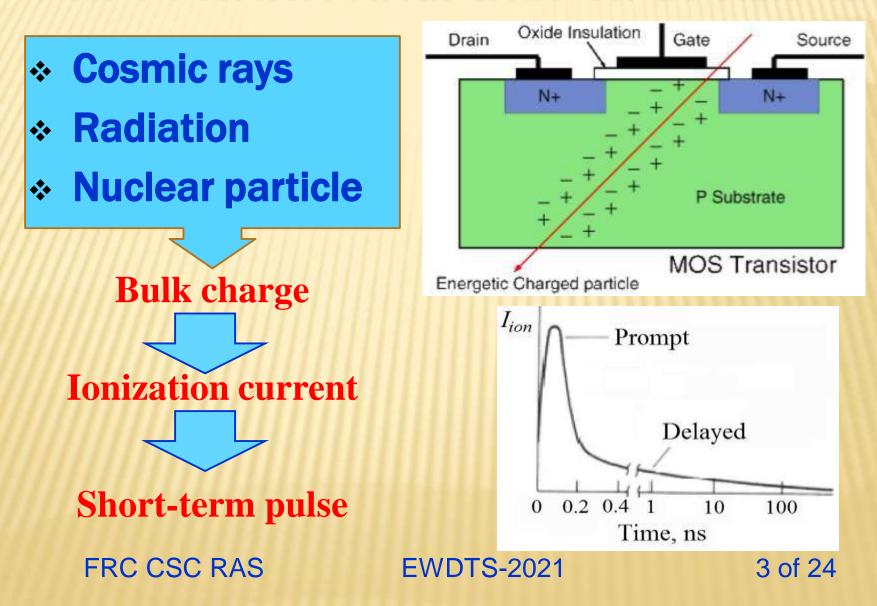

## **SOFT ERROR PHYSICAL REASONS (1)**

## **SOFT ERROR PHYSICAL REASONS (2)**

BA

$\boldsymbol{C}_{AX}$

A1

- Electromagnetic pulses

- Noise

- Signal cross-talk

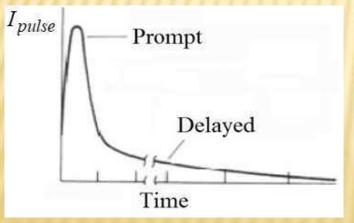

### Short-term pulse

FRC CSC RAS

**EWDTS-2021**

4 of 24

V<sub>DD</sub>

V<sub>SS</sub>

$\mathbf{C}_{\mathrm{AX}}$

A2

*Substrate*

Х

$\mathbf{C}_{\mathrm{X}}$

FRC CSC RAS

**EWDTS-2021**

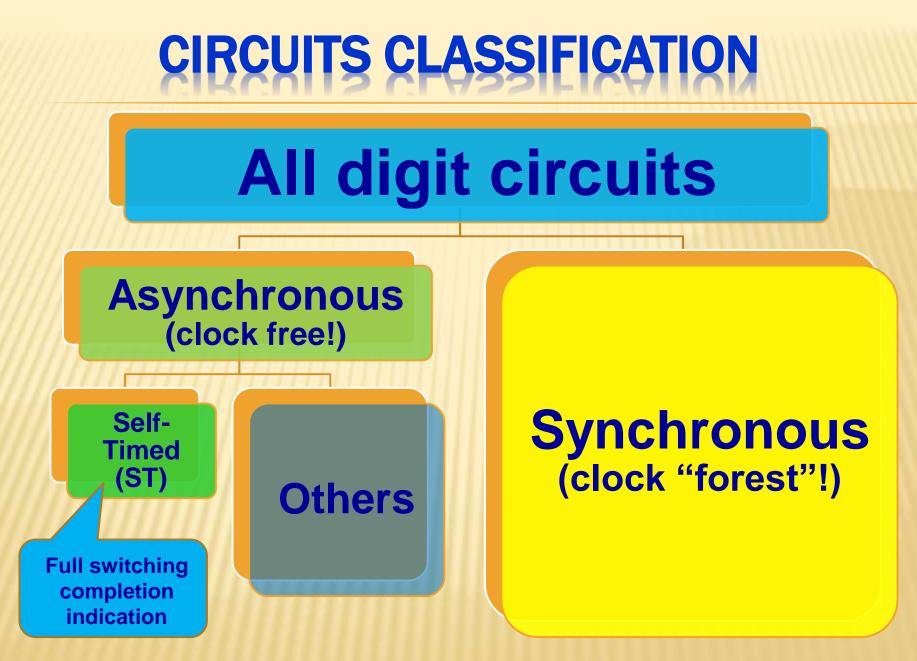

# **SELF-TIMED PRINCIPLES**

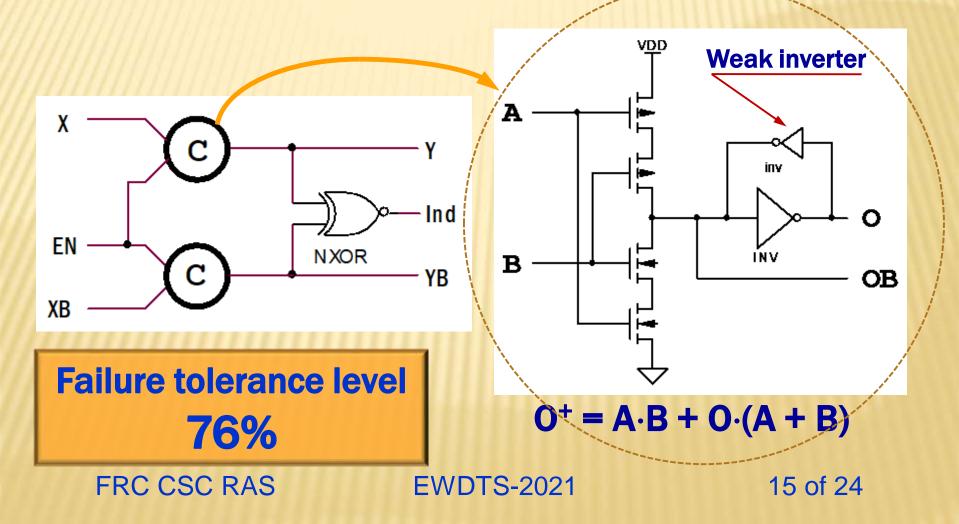

Two operation phase: \* work phase (data processing) \* spacer (pause) Redundant information signal coding (dual-rail) Full indication of all circuit's cells in each operation phase

Higher level of soft error tolerance than in synchronous circuits Soft error

tolerance level:

76%

FRC CSC RAS

**EWDTS-2021**

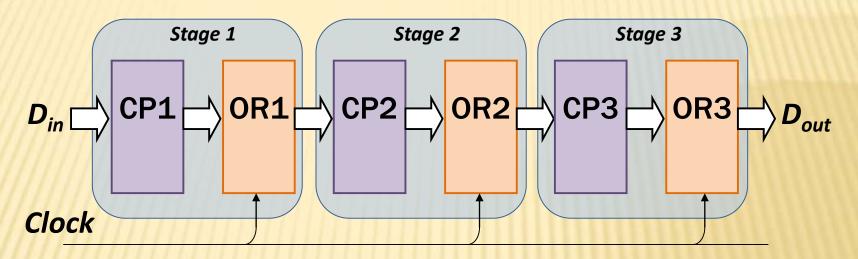

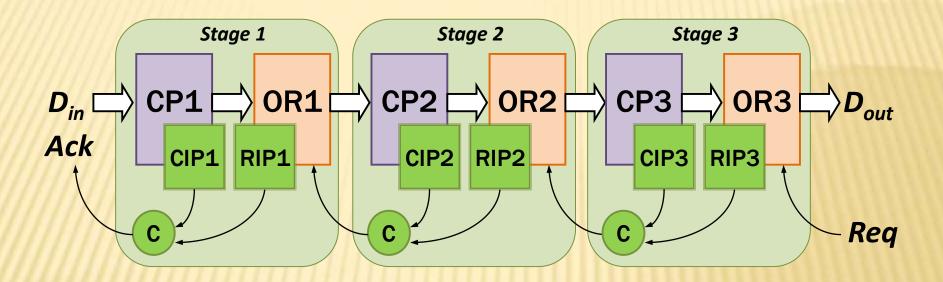

## SYNCHRONOUS PIPELINE

**CP – Combinational Part; OR – Output Register**

### **Draw-backs:**

- Worst case performance

- Complex clock tree (up to 30% of total power consumption)

FRC CSC RASEWDTS-2021

## **SELE-TIMER PIPELINE**

### **Draw-backs:**

- Hardware redundancy (1.5 3 times)

- Performance depends on data width

FRC CSC RAS EWDTS-2021

## SOFT ERROR IN SYNCHRONOUS CIRCUITS

### Soft error can appear

FRC CSC RAS

**EWDTS-2021**

# SOFT ERROR IN SELF-TIMED CIRCUITS

#### Soft error can appear

FRC CSC RAS

**EWDTS-2021**

# SOFT ERROR IN SELF-TIMED CIRCUITS

### Soft error is masked

FRC CSC RAS

**EWDTS-2021**

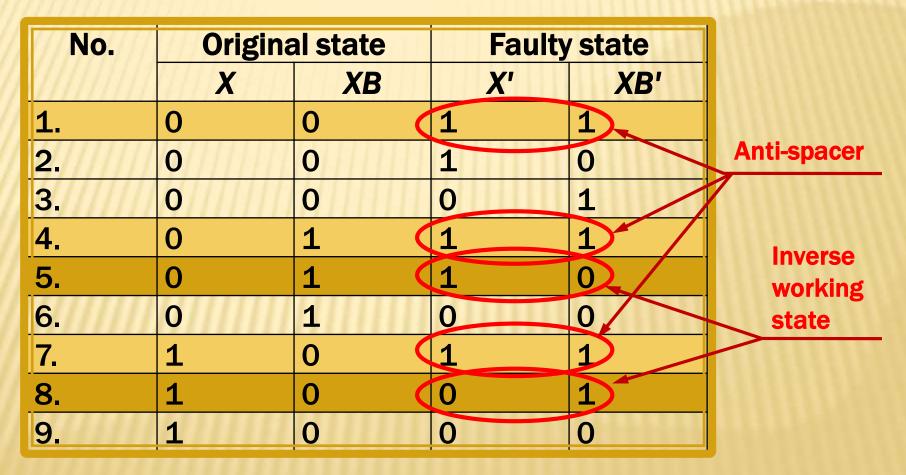

# SOFT ERROR TYPES IN ST CIRCUITS

#### For dual-rail signal (X, XB) with null spacer:

FRC CSC RAS

**EWDTS-2021**

# **CRITICAL SOFT ERRORS**

Inverse working state (multiple soft error) **One can prevent it by layout techniques:** 1) place dual-rail signal components' drivers far enough from each other, 2) rout dual-rail components' wires close to each other. Anti-spacer (multiple or single soft error) One can mask it by circuitry techniques.

FRC CSC RAS

**EWDTS-2021**

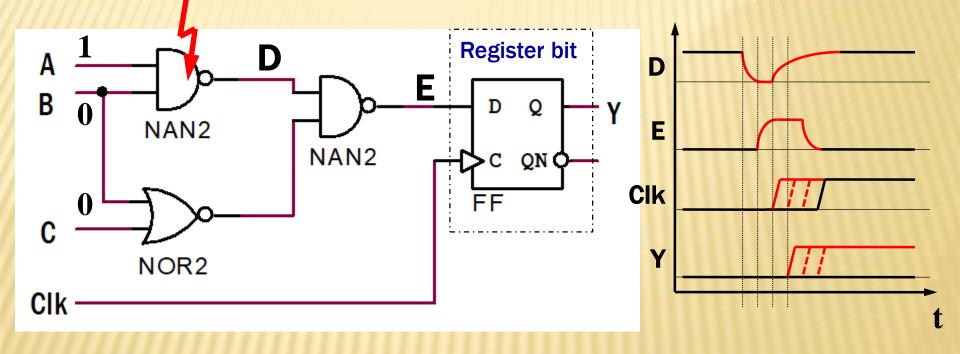

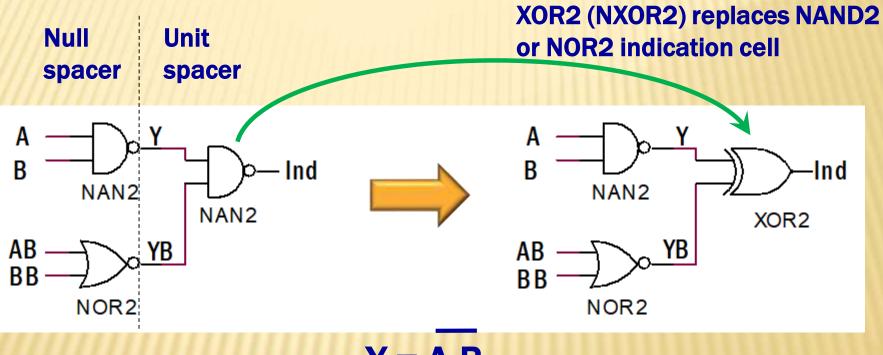

## FAILURE TOLERANCE IMPROVEMENT TECHNIQUES (1)

#### **Indicating anti-spacer as spacer**

$Y = A \cdot B$

FRC CSC RAS

**EWDTS-2021**

## FAILURE TOLERANCE IMPROVEMENT TECHNIQUES (2)

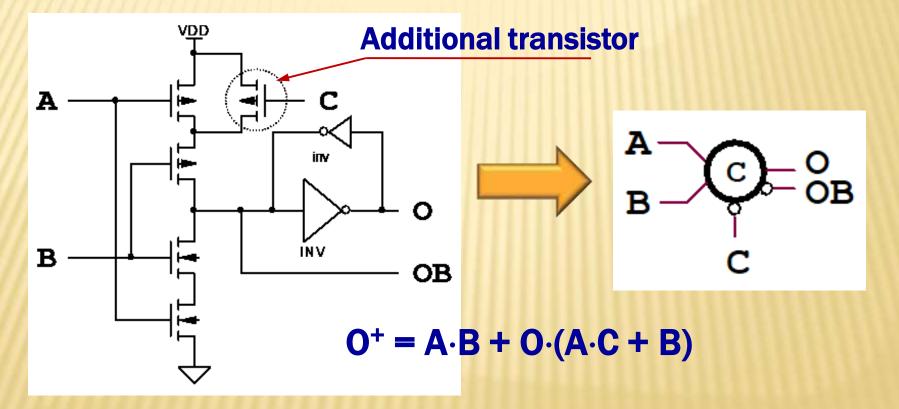

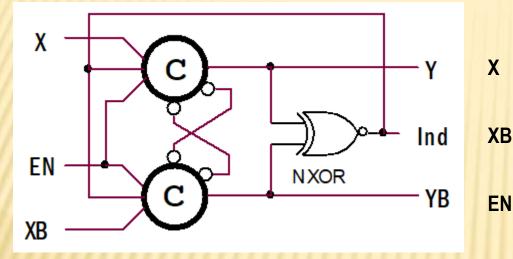

#### **Register bit**

#### **Muller's C-element**

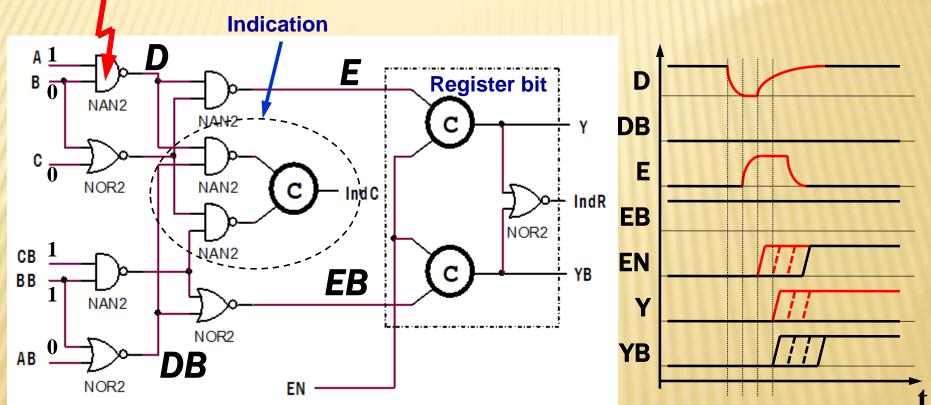

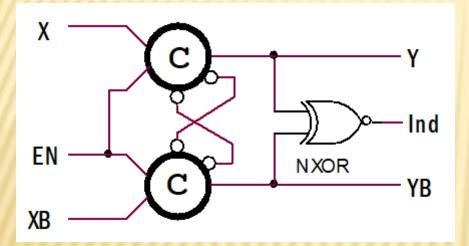

## FAILURE TOLERANCE IMPROVEMENT TECHNIQUES (3)

**Convenient self-timed register bit**

**Input anti-spacer**

## FAILURE TOLERANCE IMPROVEMENT TECHNIQUES (4)

#### **C-element protected against sticking in anti-spacer**

FRC CSC RAS

**EWDTS-2021**

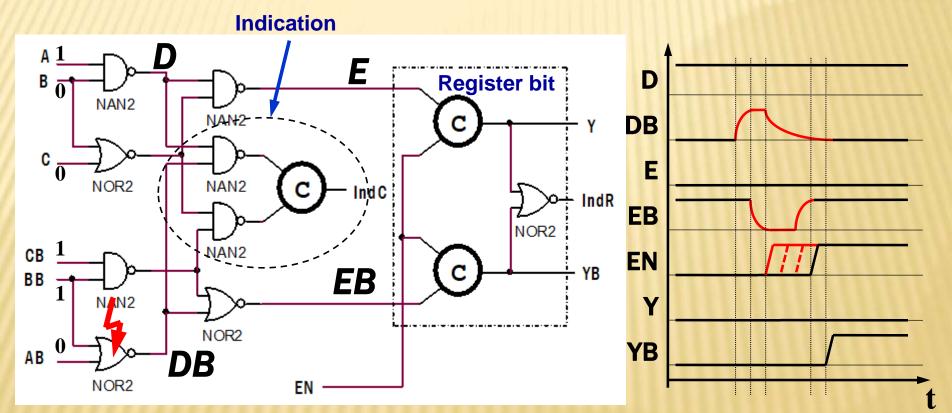

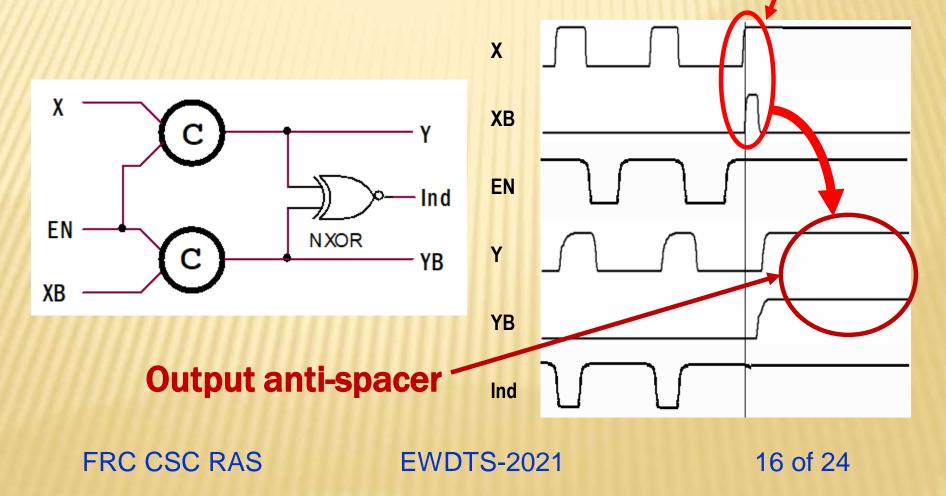

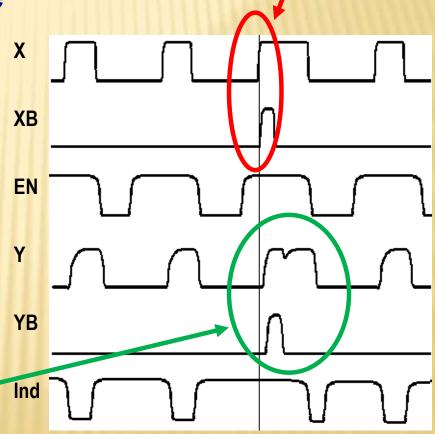

### FAILURE TOLERANCE IMPROVEMENT TECHNIQUES (5)

# **Register bit protected against sticking in anti-spacer state**

**Input anti-spacer**

Register bit does not stick in anti-spacer FRC CSC RAS EWD

EWDTS-2021

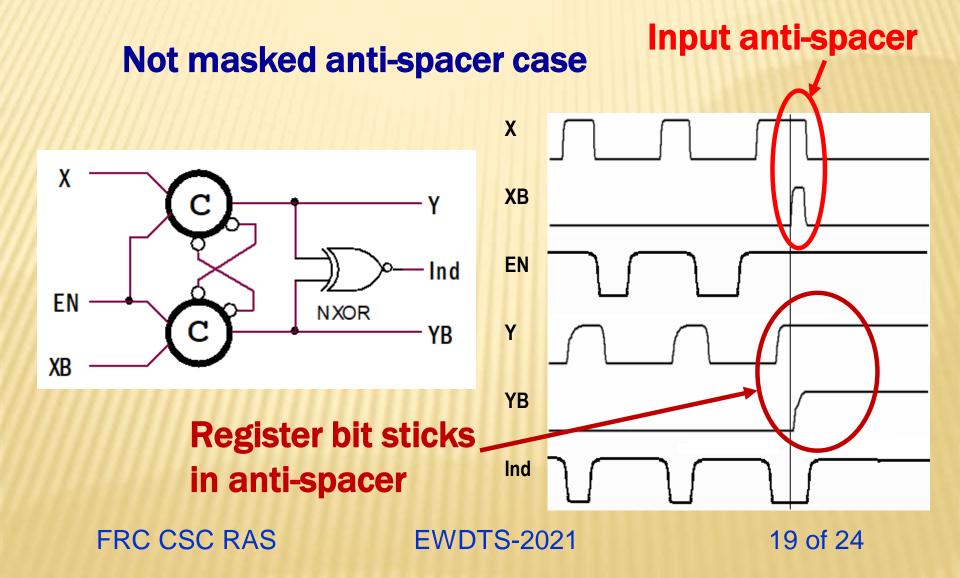

## FAILURE TOLERANCE IMPROVEMENT TECHNIQUES (6)

## FAILURE TOLERANCE IMPROVEMENT TECHNIQUES (7)

#### **Resilient register bit**

Feedback from output "Ind" protects writen correct state against switching to the anti-spacer FRC CSC RAS

**EWDTS-2021**

Y

YB

Ind

20 of 24

Input

anti-spacer

## FAILURE TOLERANCE IMPROVEMENT TECHNIQUES (8)

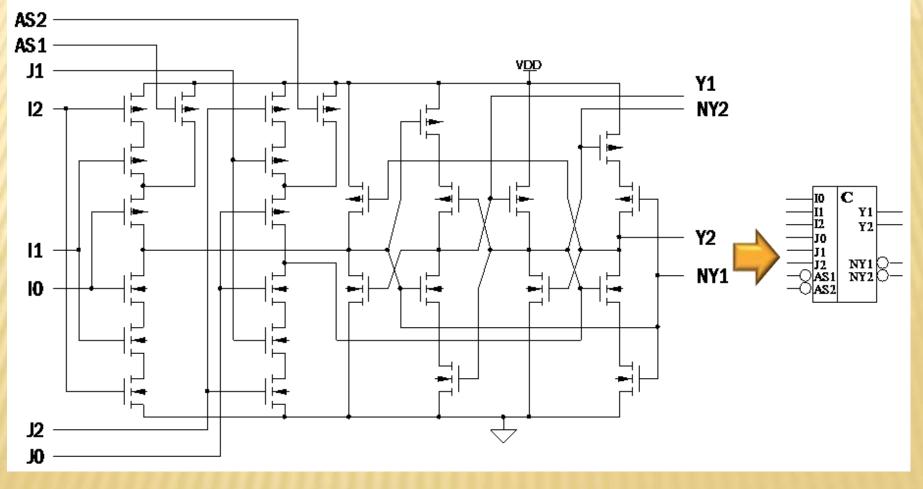

#### **DICE-like C-element masks any inside soft error**

FRC CSC RAS

**EWDTS-2021**

## FAILURE TOLERANCE IMPROVEMENT TECHNIQUES (9)

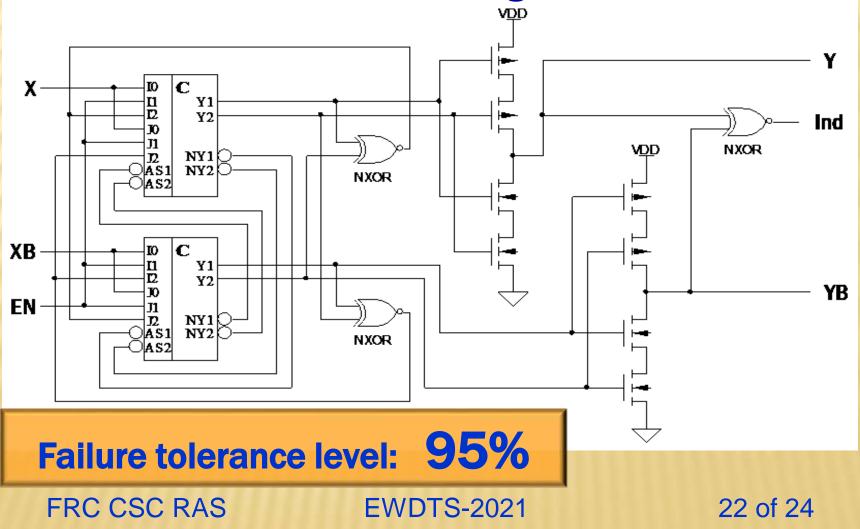

#### **DICE-like fail-safe register bit**

- The proposed layout techniques reduce the number of soft error types in ST circuits

- The circuitry techniques, including crossconnections and local feedback, prevent the ST pipeline register from sticking in the antispacer state

- The use of a DICE-like C-element ensures the register bit's immunity to soft errors inside it

- All proposed techniques improve the ST circuit's soft error tolerance level from 76% to 95%

FRC CSC RAS

**EWDTS-2021**

- Director: academician Sokolov I.A.

- Address: Institute of Informatics Problems of the Federal Research Center "Computer Science and Control" of the Russian Academy of Sciences (IPI RAS), Moscow, Russian Federation, 119333, Vavilov str., 44, b.2

- Tel: +7 (495) 137 34 94

- Fax: +7 (495) 930 45 05

- E-mail: <u>ISokolov@ipiran.ru</u>

- Stepchenkov Y.A., tel. +7 (495) 671 15 20, Ystepchenkov@ipiran.ru

FRC CSC RAS

**EWDTS-2021**